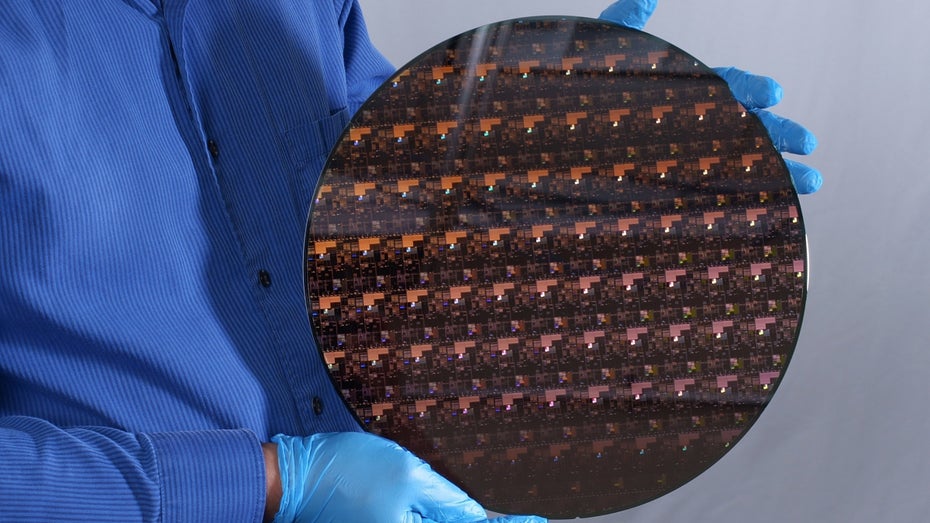

IBM präsentiert einen Wafer, der mit der neuen Zwei-Nanometer-Methode des konzerneigenen Forschungslabors gefertigt worden ist. (Bild: IBM Research)

45 Prozent mehr Leistung und 75 Prozent weniger Energieverbrauch soll die neue Technologie von IBM im Vergleich zur Sieben-Nanometer-Konkurrenz bringen. Das verspricht das konzerneigene Forschungslabor IBM Research in seiner Pressemitteilung. Der Durchbruch sei für die gesamte Halbleiterindustrie von großer Bedeutung. Die Verfasser zählen eine Reihe an Vorteilen für Produkte, Mensch und Umwelt auf.

Hohe Beschleunigung bei niedrigerem CO2-Abdruck

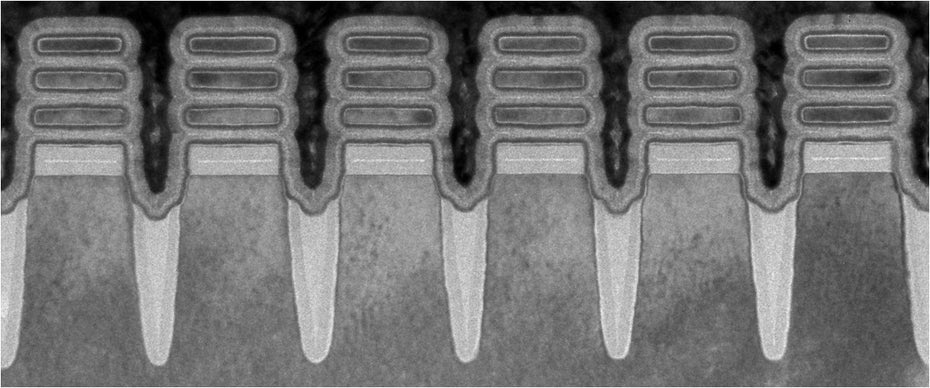

So sei eine Vervierfachung der Akkulaufzeit von Mobiltelefonen durch die Chips möglich. Zudem könnten Rechenzentren ihren CO2-Fußabdruck erheblich verkleinern. Nicht zuletzt winke eine „drastische Beschleunigung“ von Laptops bis hin zu einem schnelleren Internetzugang. Zudem könnten autonom-fahrende Fahrzeuge von einer schnelleren Objekterkennung und Reaktionszeit profitieren. Das Forschungslabor in Albany (USA) hat die Leistungssteigerung durch das Verwenden der Nanosheet-Technologie erreicht. Bei ihr legten die Experten drei Materialschichten aufeinander, deren Stapel NMOS- und PMOS-Transistoren übereinander statt bisher nebeneinander anordnen. Wann die Technologie marktreif sein könnte, vermögen die Verfasser nicht zu sagen. Experten gehen von 2023 aus. IBMs eigene Serie basiert ihrer Vermutung nach erst 2026 auf dem neuen Prozess. Die Fachleute schätzen den Herstellungsaufwand der Zwei-Nanometer-Chips mit der nun vorgestellten Methode als niedriger ein als bei aktuellen Sieben-Nanometer-Halbleitern.

IBM hat die Transitoren bei dem neuen Zwei-Nanometer-Verfahren in Stapel übereinander gepackt. (Bild: IBM Research)

„2-nm“ ist ein Marketingbegriff

IBM hatte auch vor vier Jahren die ersten Fünf-Nanometer-Wafer angekündigt. Jedoch verfügt der Konzern nicht über die Möglichkeiten, die eigenen Designs in Serie zu produzieren. Die neusten Sieben-Nanometer-Prozessoren „Power10“ etwa fertigt Samsung für den Konzern. The Register betont, „2-nm“ sei eine Namenskonvention, um zu zeigen, dass der Prozessorknoten kleiner ausfalle als beim herkömmlichen Fünf-Nanometer-Design. Tatsächlich sei keine Komponente wirklich zwei Nanometer groß. Das Transistor-Gate besitzt eine Länge von zwölf Nanometern. Im Vergleich ist Intels 14-Nanometer-Gate 20 Nanometer lang, Samsungs Sieben-Nanometer-Knoten misst acht bis zehn Nanometer. Eine weitere Zahl hilft bei der Einordnung: 50 Milliarden Transistoren sollen mit der neuen Methode auf einen 150 Quadratmillimeter großen Die passen. Das entspräche 333 Millionen Transistoren pro Quadratmillimeter. Bei TSMCs Fünf-Nanometer-Prozess sind es 170, bei Intels Zehn-Nanometer-Verfahren 100 Millionen Transistoren. IBM hat erst kürzlich eine Fertigungspartnerschaft mit dem Prozessor-Marktführer geschlossen. Beobachter gehen davon aus, dass der US-Hersteller als Option dient, falls Samsung nicht liefern kann.

Bitte beachte unsere Community-Richtlinien

Wir freuen uns über kontroverse Diskussionen, die gerne auch mal hitzig geführt werden dürfen. Beleidigende, grob anstößige, rassistische und strafrechtlich relevante Äußerungen und Beiträge tolerieren wir nicht. Bitte achte darauf, dass du keine Texte veröffentlichst, für die du keine ausdrückliche Erlaubnis des Urhebers hast. Ebenfalls nicht erlaubt ist der Missbrauch der Webangebote unter t3n.de als Werbeplattform. Die Nennung von Produktnamen, Herstellern, Dienstleistern und Websites ist nur dann zulässig, wenn damit nicht vorrangig der Zweck der Werbung verfolgt wird. Wir behalten uns vor, Beiträge, die diese Regeln verletzen, zu löschen und Accounts zeitweilig oder auf Dauer zu sperren.

Trotz all dieser notwendigen Regeln: Diskutiere kontrovers, sage anderen deine Meinung, trage mit weiterführenden Informationen zum Wissensaustausch bei, aber bleibe dabei fair und respektiere die Meinung anderer. Wir wünschen Dir viel Spaß mit den Webangeboten von t3n und freuen uns auf spannende Beiträge.

Dein t3n-Team