ARM-Konter von Intel: Lakefield ist da

Wafer mit Lakefield-SoC. (Bild: Intel)

Nach vielen Verzögerungen hat Intel seine vor anderthalb Jahren angekündigten, intern Lakefield genannten Systems-on-a-Chip vorgestellt. Die SoC kombinieren unterschiedliche x86-Kerne sowie eine Grafikeinheit plus I/O-Funktionen und Arbeitsspeicher in einem einzigen Package. Das Sieben-Watt-Design ist für besonders leichte Ultrabooks oder Foldable-Convertibles gedacht.

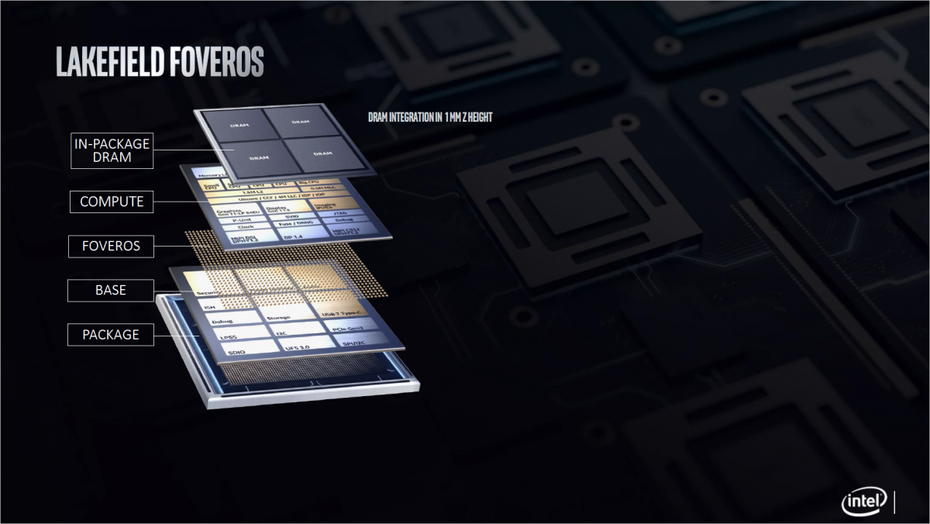

Vorerst wird es zwei Versionen geben, den Core i5-L16G7 und den Core i3-L13G4. Beide weisen fünf CPU-Kerne auf und integrieren acht Gigabyte LPDDR4X-Speicher, wobei es für Partner auch Ableger mit weniger – nicht aber mehr – RAM geben soll. Der Core i5-L16G7 und der Core i3-L13G4 unterscheiden sich bei den Taktraten für Cores und Grafikeinheit, das grundsätzliche Design hingegen ist identisch. Die technische Basis sind insgesamt vier Chips, die Intel im 3D-Verfahren namens Foveros stapelt.

Performance-Core auf Ice-Lake-Basis

Ganz unten befindet sich ein per 22FFL-Verfahren (P1222) produziertes I/O-Die, das Funktionen wie PCIe Gen3 und UFS 3.0 sowie USB 3.2 Gen1 mitbringt. Der Chip misst 92 Quadratmillimeter bei 650 Millionen Transistoren. Darüber befindet sich das eigentliche Compute-Die, das im Zehn-Nanometer-Prozess (P1274) gefertigt und per TSV durchkontaktiert wird. Es umfasst fünf CPU-Kerne sowie die Gen11-Grafikeinheit und den 64-Bit-Speichercontroller. Der schnelle Performance-Core basiert auf der Sunny-Cove-Architektur, wie sie von Ice Lake bekannt ist; im Falle von Lakefield allerdings ohne Hyperthreading für zwei logische Kerne/Threads. Hinzu kommen vier Efficiency-Cores mit Tremont-Technik; die wird auch bei den kommenden Atom-Chips verwendet. Das Compute-Die bringt 4,05 Milliarden Transistoren auf 82 Quadratmillimetern unter. Auf den beiden Intel-Chips sitzen oben noch zwei Schichten an LPDDR4X-Speicher, das komplette Package misst 12 x 12 x 1 Millimeter.

| Kerne | Takt | Boost (Sunny) | Boost (Tremont) | Grafik | Speicher | TDP | |

|---|---|---|---|---|---|---|---|

| Core i5-L16G7 | 1+4 | 1,4 bis 1,8 GHz | 3,0 GHz | 2,8 GHz | 64 EUs @ 500 MHz | LPDDR4X-4266 | 7 Watt |

| Core i3-L13G4 | 1+4 | 0,8 bis 1,3 GHz | 2,8 GHz | 2,6 GHz | 48 EUs @ 500 MHz | LPDDR4X-4266 | 7 Watt |

Eine Herausforderung ist das Verteilen von Threads: Solche, die viel Leistung erfordern, werden auf die Sunny-Cove-Kerne gelegt und Hintergrund-Tasks arbeiten die Tremont-Cores ab. Intel zufolge wird das durch eine Mischung aus Hard- und Firmware sowie den Scheduler des Betriebssystems (Windows 10) gelöst. Wann die SC- und wann die TNT-Kerne übernehmen, hängt davon ab, ob die jeweilige Anwendung eher Singlethreading- oder doch mehr Multithreading-lastig ist. Im ARM-Segment ist eine Big-Little-Aufteilung seit Jahren etabliert, Microsoft konnte mit Chips wie dem Snapdragon 8cx mit 4x A76 und 4x A55 bereits Erfahrung sammeln. Ins Detail ging Intel vorab nicht, so bleibt auch unklar, ob der Sunny-Cove-Kern etwa AVX(2) unterstützt. AVX-512 wurde zugunsten der Die-Fläche wohl entfernt.

HC19-Präsentation zu Lakefield. (Bild: Intel)

Laut Intel soll Lakefield eine Standby-SoC-Power von nur 2,5 Milliwatt aufweisen – unter Last sind es die typischen sieben Watt wie bei Amber Lake Y. Verglichen mit einem zweikernigen Core i7-8500Y soll der Core i5-L16G7 im Browser-Benchmark WebXPRT3 eine um 24 Prozent höhere Leistung pro Watt erzielen; die Singlethread-Performance in Spec_CPU2006 (Integer) soll zwölf Prozent besser sein. Für die Grafikleistung gibt Intel ein Plus von 70 Prozent im 3DMark 11 an, was bei 64 EUs gegen 24 EUs nicht überrascht. Der Core i3-L13G4 hat nur 48 EUs, weshalb hier die Steigerung deutlich geringer ausfallen dürfte.

Zu den ersten Geräten mit Lakefield zählen das Thinkpad X1 Fold von Lenovo und das Galaxy Book S von Samsung, von Microsofts Surface Neo sagte Intel nichts. Für die Zukunft sieht der Hersteller vor, das I/O-Basis-Die mit zehn Nanometern Foveros (P1274.FV) und das Compute-Die mit sieben Nanometern (P1276) zu fertigen. Danach stehen sieben Nanometer (P1276.FV) und fünf Nanometer (P1278) auf dem Plan. Für Intel ist Lakefield ein wichtiger Schritt, da Apple mit Kalamata und Qualcomm mit weiteren Snapdragons den Ultrabook-Markt verstärkt beliefern wollen.

Autor des Artikels ist Marc Sauter.